فلیپ فلاپ T نوع دیگری از مدارهای منطقی متوالی دوپایایی است که در مدار فلیپ فلاپ کلاک قبلی JK است. فلیپ فلاپ Tرا می توان به عنوان یک عنصر دیجیتال پایه برای ذخیره یک بیت از اطلاعات، به عنوان تقسیم بر دو یا به عنوان شمارنده استفاده کرد.

فلیپ فلاپ T دارای یک ورودی واحد و یک یا دو خروجی مکمل Q و Q بار هستند که در لبه مثبت (لبه بالارونده) یا لبه منفی (لبه در حال سقوط) سیگنال ساعت ورودی یا پالس تغییر حالت می دهند.در این سری از مقالات اسکای تک به بررسی مدار فلیپ فلاپ T می پردازیم.

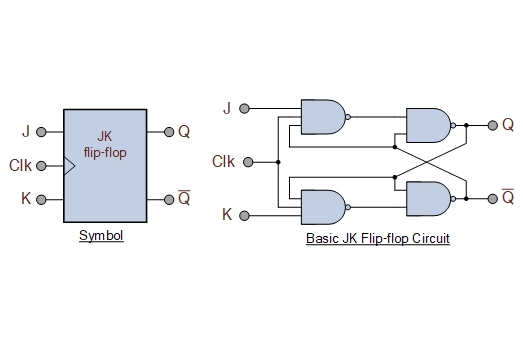

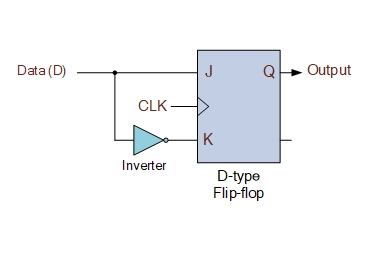

فلیپ فلاپ های Toggle، TFF یا به سادگی “فلیپ فلاپ T” به عنوان یک تراشه منطقی اختصاصی TTL یا CMOS به صورت تجاری در دسترس نیستند، آن ها را می توان به راحتی با اتصال ورودی های J و K یک فلیپ فلاپ اصلی JK در جایی که به یکدیگر متصل کرد، ساخت. ورودی J مانند دستور Set (S) و ورودی K مانند دستور Reset (R) عمل می کند.

در آموزش قبلی به یاد داشته باشیم که فلیپ فلاپ JK به عنوان یک فلیپ فلاپ ناهمزمان طبقه بندی می شود که در آن شرایط ورودی آن (HIGH یا LOW) و وضعیت حالت پایدار فعلی آن، هر دو وضعیت سوئیچینگ بعدی آن را تعیین می کنند.

فلیپ فلاپ JK را می توان به عنوان یک فلیپ فلاپ “جهانی” طبقه بندی کرد، زیرا می توان آن را پیکربندی کرد و از آن برای تکرار عمل سوئیچینگ انواع دیگر فلیپ فلاپ ها بسته به حالت های منطقی اعمال شده در ورودی های J و K آن استفاده کرد. اما قبل از اینکه با جزئیات بیشتری به فلیپ فلاپ T نگاه کنیم، اجازه دهید ابتدا مدار فلیپ فلاپ اولیه JK و عملکرد سوئیچینگ را یادآوری کنیم.

مدار بالا پیکربندی اولیه یک فلیپ فلاپ JK را با استفاده از چهار گیت NAND نشان میدهد، اما آنها همچنین میتوانند با استفاده از گیتهای NOR ساخته شوند. فلیپ فلاپ JK دارای سه ورودی با برچسب J، K و ساعت (CLK) است. ورودی داده J، (که مربوط به Set است) همراه با بازخورد از Q به گیت NAND 3 ورودی بالایی اعمال می شود، در حالی که ورودی داده دیگر K، (که مربوط به Reset است) و اتصال بازخورد Q به گیت NAND 3 ورودی پایینی اعمال می شود.

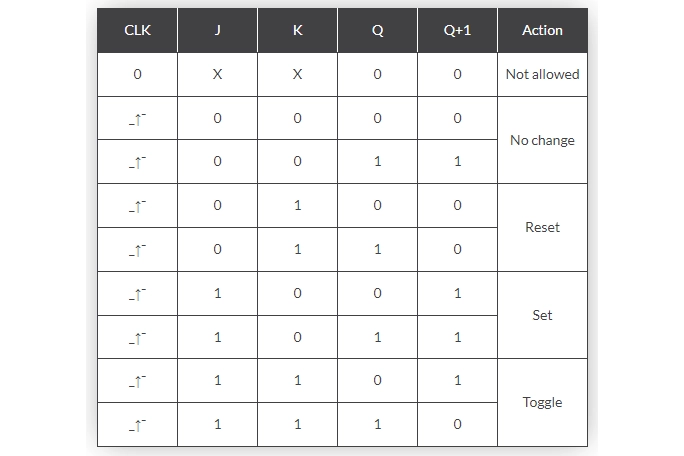

اگر ورودی های J و K هر دو LOW باشند، (J = K = 0)، مهم نیست که چند بار پالس ساعت اعمال شود، در Q تغییری ایجاد نخواهد شد. اگر J = 0 (LOW) و K = 1 (HIGH) لبه ساعت بعدی Q خروجی LOW را تنظیم مجدد می کند (Q = 0). اگر J = 1 و K = 0، آنگاه لبه ساعت بعدی خروجی Q را HIGH (Q = 1) تنظیم می کند.

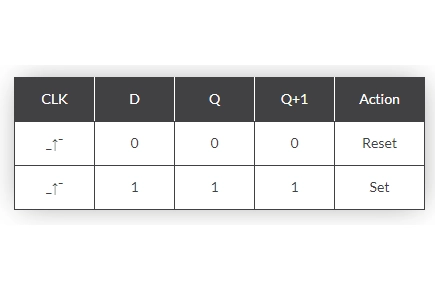

که در آن: X به معنای “مهم نیست”، “0” یا “1” است، و _↑¯ لبه صعودی مثبت پالس ساعت است.

جایی که: Q حالت ثابت فعلی فلیپ فلاپ را نشان می دهد و Q+1 حالت سوئیچینگ بعدی است.

مشکل اینجاست که اگر هر دو ورودی داده J و K در منطق “1”، هم زمان HIGH باشند (J = K = 1)، وقتی ورودی ساعت (CLK) HIGH می شود، خروجی های آن تغییر می کند و حالت یکدیگر را تکمیل می کند. اما همانطور که خروجی ها بازخورد داده می شوند، خروجی ها پس از یک بار تکمیل شدن، به طور مداوم تغییر حالت می دهند و باعث می شود خروجی در Q بین تنظیم و تنظیم مجدد در نوسان باشد.

بنابراین، فلیپ فلاپهای JK به طور کلی با استفاده از پیکربندیهای اصلی گیت NAND یا NOR همانطور که در بالا نشان داده شده است ساخته نمیشوند، بلکه در عوض برای تشکیل فلیپ فلاپهای پیشرفتهتر master-slave (لبه راهاندازی) ساخته میشوند که ذاتاً بسیار پایدارتر هستند.

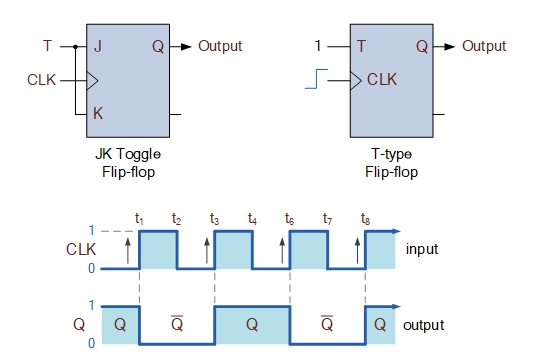

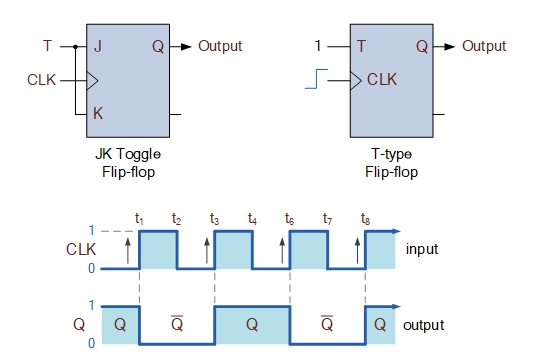

در حالی که فلیپ فلاپ داده (D) یک تغییر از یک فلیپ فلاپ SR کلاک شده است که با استفاده از گیت های NAND یا NOR ساخته شده است، فلیپ فلاپ Toggle (T) یک تغییر از فلیپ فلاپ ساعت شده JK است. فلیپ فلاپ T نام خود را از این واقعیت گرفته است که دو خروجی Q و Q باراز حالت قبلی خود معکوس می شوند زیرا هر بار که راه اندازی می شود به جلو و عقب می چرخد (T = 1).

یعنی خروجیهای Q و Qبار اگر 0 بود به 1 و اگر قبلاً 1 بود به 0 تغییر میکنند، اما فقط زمانی که ورودی T تغییر HIGH کند، در غیر این صورت تغییر نمیکنند. و این عمل تغییر ناهمزمان است که ما در اینجا به آن علاقه مندیم. JK برای فلیپ فلاپ T یا Toggle تغییر نام داده می شود و به طور کلی با منطق یا نماد گرافیکی نشان داده شده نشان داده می شود. نماد شماتیک Toggle دو ورودی در دسترس دارد، یکی نشان دهنده ورودی «ضامن» (T) و دیگری ورودی «ساعت» (CLK) است.

همچنین، درست مانند فلیپ فلاپ 74LS73 JK، نوع T را نیز می توان به گونه ای پیکربندی کرد که دارای یک ورودی فعال به نام EN یا CE (فعال ساعت) باشد که به آن اجازه می دهد آخرین وضعیت داده ذخیره شده در خروجی های خود را به طور نامحدود نگه دارد.

بنابراین با مجموعه ورودی فعال ساعت، استفاده از هر پالس ساعت جدید از تغییر وضعیت خروجی ها جلوگیری می کند. اما این ویژگی «فعال کردن»، در صورت نیاز، باید با استفاده از گیتهای منطقی اضافی اعمال شود.

مثلث شورون در ورودی هر یک از انواع فلیپ فلاپ T نشان می دهد که یک دستگاه لبه گردان است. اگر یک حباب یا دایره کوچک در ورودی وجود داشته باشد، نشان می دهد که فلیپ فلاپ روی لبه سقوط منفی (بالا به پایین) هر پالس تغییر می کند.در غیر این صورت، روی لبه انتقالی مثبت یا بالارونده (کم به بالا) هر پالس ورودی تغییر حالت می دهد.

سپس میتوانیم مدار منطقی یک فلیپ فلاپ T تک بیتی را با استفاده از فلیپ فلاپ اصلی JK با اتصال ورودیهای داده J و K به هم بسازیم، جایی که نقطه مشترک در اتصال دو ورودی T تعیین شده است، همانطور که نشان داده شده است.

فرض کنید در ابتدا CLK و ورودی T هر دو LOW هستند (CLK = T = 0) و خروجی Q HIGH (Q = 1) است. در لبه بالارونده یا لبه نزولی یک پالس CLK، شرط منطقی “0” موجود در T از تغییر حالت خروجی در Q جلوگیری می کند. بنابراین زمانی که T = 0 باشد، خروجی بدون تغییر باقی میماند.

حال فرض میکنیم که ورودی T HIGH (T = 1) و CLK LOW (CLK = 0) باشد. در لبه بالارونده (با فرض انتقال مثبت) یک پالس CLK در زمان t1، خروجی در Q تغییر حالت می دهد و LOW می شود و Q بالا می شود. انتقال منفی پالس ساعت از HIGH به LOW در زمان t2 هیچ تاثیری بر خروجی در Q ندارد زیرا فلیپ فلاپ به یک حالت پایدار بازنشانی میشود.

در لبه افزایشی بعدی سیگنال ساعت در زمان t3، منطق “1” در T به Q منتقل می شود و حالت آن را تغییر می دهد و خروجی Q HIGH را دوباره تغییر می دهد. انتقال منفی پالس CLK در زمان t4 از HIGH به LOW یک بار دیگر تأثیری بر خروجی ندارد. بنابراین خروجی Q فلیپ فلاپ در هر لبه مثبت (برای مثال) پالس CLK تغییر می کند.

علاوه بر فلیپ فلاپهای JK دو پایدار، ما همچنین میتوانیم با استفاده از فلیپ فلاپهای نوع D یا Delay که از یک اصلاح ساده در مدار JK کلاکشده ساخته شدهاند، یک کنش جابجایی ایجاد کنیم. فلیپ فلاپ نوع D دارای دو ورودی D (داده) و CLK (ساعت) است و در پاسخ به انتقال لبه مثبت یا منفی در ورودی ساعت تغییر حالت می دهد. فلیپ فلاپ نوع D همچنین می تواند برای ذخیره سازی موقت یک بیت از اطلاعات مانند فلیپ فلاپ T استفاده شود.

افزودن یک اینورتر (NOT gate) بین پایانه های J و K و جایگزینی آنها با تنها یک ورودی D (برای داده). این بدان معنی است که آنها هرگز نمی توانند مقدار دیجیتال یکسانی داشته باشند زیرا اگر ورودی J = 0، سپس K = 1، به همین ترتیب اگر J = 1، سپس K = 0. مزیت در اینجا این است که گنجاندن اینورتر بین J و K منجر به مقدار خروجی در Q به دنبال مقدار ورودی D (0 یا 1) هر زمان که ساعت (Clk) HIGH باشد، منطق “1” است و ما می توانیم این را در جدول سوئیچینگ زیر نشان دهیم.

که در آن Q حالت فعلی و Q+1 حالت بعدی پس از اعمال یک پالس ساعت است. سپس می توانیم عمل سوئیچینگ فلیپ فلاپ نوع D را به شکل بولی به صورت زیر تعریف کنیم:

Q+1 = D

بنابراین وضعیت حالت پایدار خروجی آن فقط با هر بار پالس شدن ورودی ساعت آن، اگر و فقط در صورتی که در ورودی داده (D) تغییری ایجاد شود، HIGH یا LOW تغییر می کند. این است که پیکربندی فلیپ فلاپ نوع D تنها به خروجی در Q اجازه می دهد تا زمانی که ساعت HIGH است، وضعیت پایداری مشابه ورودی D را داشته باشد. نقطه ضعف در اینجا این است که ما به دو ورودی جداگانه D و Clk نیاز داریم تا آن را تغییر دهیم. سپس به روشی نیاز داریم که خروجی Q آن را با اعمال هر پالس ساعت به حالت مخالف تغییر دهیم، یعنی جابجایی.

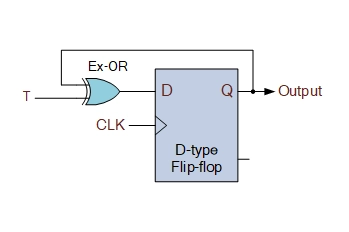

در بالا دیدیم که عبارت بولی که برای عمل سوئیچینگ یک فلیپ فلاپ T داده شده است، می تواند بیانگر یک گیت انحصاری-OR به صورت Q+1 = Q ⊕ T باشد.سپس میتوانیم یک گیت منطقی انحصاری-OR اضافه کنیم تا فلیپ فلاپ نوع D داده شده را به فلیپ فلاپ T تبدیل کنیم.

در اینجا، “T” به یکی از ورودی های یک گیت انحصاری OR 2 ورودی تبدیل می شود در حالی که خروجی Q برای تبدیل شدن به دیگری بازخورد داده می شود. بنابراین T و Q هر دو ورودیهای گیت Ex-OR برای تولید عبارت بولی مورد نیاز برای هدایت ورودی D هستند. اگر T = 0، خروجی گیت انحصاری-OR که Q ⊕ T است نیز LOW (0) خواهد بود، بنابراین فلیپ فلاپ نوع D در یک حالت پایدار ثابت می ماند.

با این حال، هنگامی که T = 1، انحصاری-OR یک تغییر حالت در D ایجاد می کند هر بار که فلیپ فلاپ نوع D کلاک می شود، زیرا خروجی Q که به گیت باز می گردد در هر پالس ساعت بین HIGH و LOW تغییر می کند. هنگامی که قرار است یک بیت داده واحد ذخیره شود، آن را به عنوان یک عنصر bistable بسیار مفید می کند.

از آنجایی که این پیکربندی فقط میتواند حالت بدون تغییر یا حالت مکمل خود را حفظ کند، هیچ راهی برای ایجاد یک حالت خروجی اولیه یا HIGH یا LOW هنگامی که برای اولین بار برق اعمال میشود، بدون افزودن ورودیهای Preset (Pre) یا Clear (Clr) یا خارجی وجود ندارد.

مدار برای مقداردهی اولیه یا تنظیم خروجی Q در یک حالت شناخته شده. همچنین، از آنجایی که خروجی در Q در لبه افزایشی هر پالس ساعت تغییر حالت می دهد، دوره زمانی خروجی در Q برابر با نصف فرکانس پالس ساعت خواهد بود. به عبارت دیگر، عمل جابجایی فلیپ فلاپ T می تواند مدار تقسیم بر دو ایجاد کند که خروجی آن نسبت علامت به فاصله 1:1 (50%) خواهد داشت، از دوره LOW و دوره HIGH از طول خروجی Q برابر است.

مزیت در اینجا این است که فلیپ فلاپ های T می توانند به عنوان شمارنده های باینری بسیار ساده یا شمارنده های موج دار برای تقسیم فرکانس (کاهش فرکانس یک شکل موج دوره ای) استفاده شوند که در آن تعداد “n” از مراحل فلیپ فلاپ T به صورت سری به هم متصل می شوند. سپس مجموعه ای از شکل موج های خروجی تولید می کند که فرکانس یا دوره ای برابر با نصف خروجی قبلی دارند.