این فلیپ فلاپ ساده JK بیشترین استفاده را در بین تمام طرحهای فلیپ فلاپ دارد و به عنوان یک مدار فلیپ فلاپ جهانی در نظر گرفته میشود. دو ورودی با برچسب “J” و “K” حروف کوتاه شده کلمات دیگر مانند “S” برای Set و “R” برای Reset نیستند.اما خود حروف مستقلی هستند که توسط مخترع آن جک کیلبی برای تشخیص طرح فلیپ فلاپ از انواع دیگر انتخابشده است.

عملکرد متوالی فلیپ فلاپ JK دقیقاً مانند فلیپ فلاپ SR قبلی با همان ورودیهای «تنظیم» و «بازنشانی» است. تفاوت این بار در این است که “JK flip flop” هیچ حالت ورودی نامعتبر یا ممنوعه SR Latch ندارد، حتی زمانی که S و R هر دو در منطق “1” هستند. در این سری از مقالات اسکای تک به بررسی مدار فلیپ فلاپ JK می پردازیم.

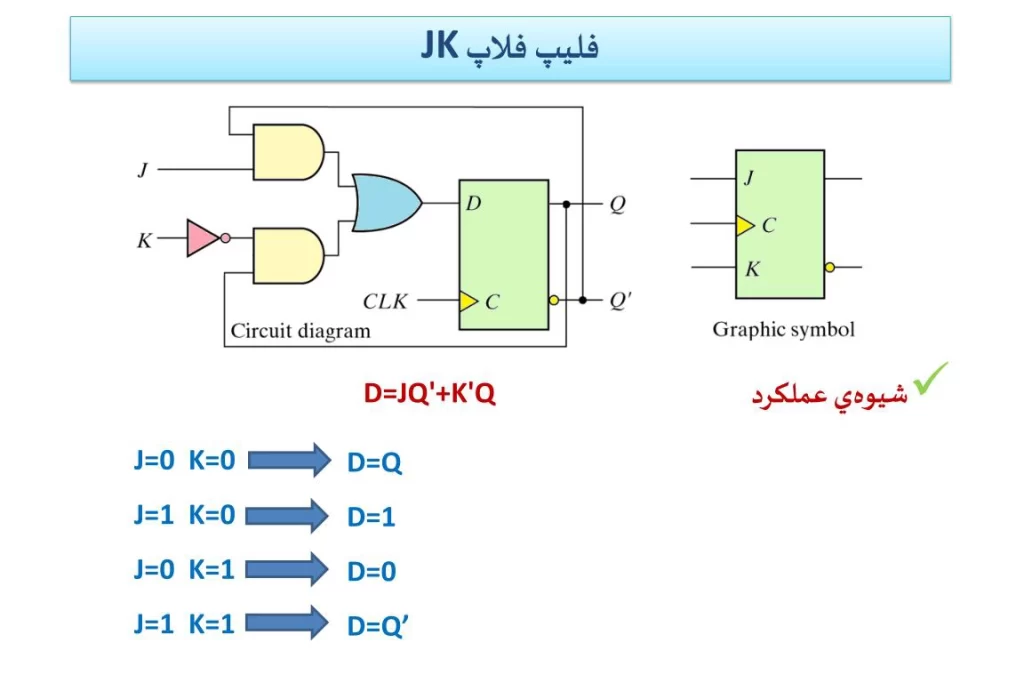

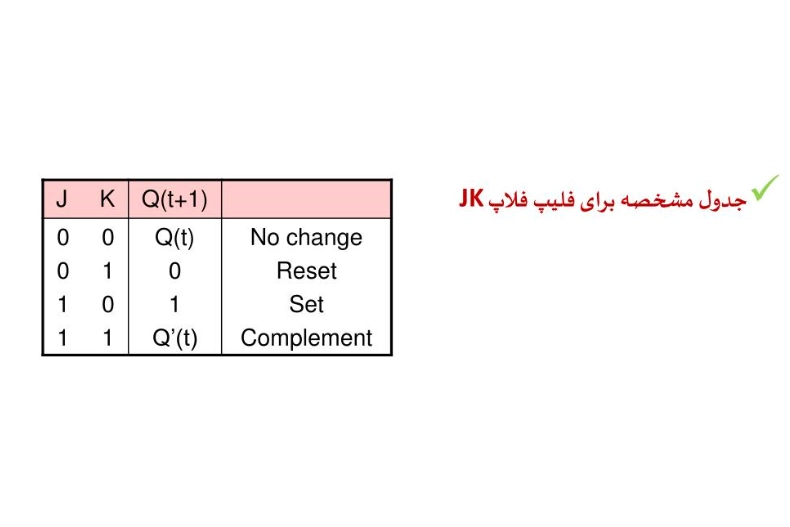

فلیپ فلاپ JK اساساً یک فلیپ فلاپ SR دردار با اضافه شدن یک مدار ورودی ساعت است که از شرایط خروجی غیرقانونی یا نامعتبر که میتواند زمانی رخ دهد که هر دو ورودی S و R برابر با سطح منطقی “1” باشند، جلوگیری میکند. با توجه به این ورودی کلاک اضافی، یک فلیپ فلاپ JK دارای چهار ترکیب ورودی ممکن “منطق 1″، “منطق 0″، “بدون تغییر” و “تغییر”است .

هر دو ورودی S و R در SR bistable قبلی با دو ورودی به نامهای ورودی J و K جایگزین شدهاند. سپس این برابر است با: J = S و K = R. دو گیت AND 2 ورودی دریچه دوپایه SR اکنون با دو گیت NAND 3 ورودی جایگزین شدهاند که ورودی سوم هر گیت به خروجیهای Q و Q بار متصل است.

این جفت متقابل فلیپ فلاپ SR اجازه میدهد تا شرایط قبلی نامعتبر از حالت S = “1” و R = “1” برای ایجاد یک “عمل تعویض” استفاده میشود زیرا دو ورودی اکنون در هم قفل شدهاند. اگر مدار اکنون “SET” باشد، ورودی J توسط وضعیت “0” Q بار از طریق گیت NAND پایینی مهار میشود. اگر مدار “RESET” باشد، ورودی K توسط وضعیت “0” Q از طریق گیت NAND بالایی مهار میشود.

از آنجایی که Q و Q بارهمیشه متفاوت هستند، میتوانیم از آنها برای کنترل ورودی استفاده کنیم. هنگامی که هر دو ورودی J و K برابر با منطق “1” باشند، فلیپ فلاپ JK همانطور که در جدول حقیقت زیر نشان داده شده است تغییر میکند.

سپس فلیپ فلاپ JK اساساً یک فلیپ فلاپ SR با بازخورد است که تنها یکی از دو پایانه ورودی خود را قادر میسازد، SET یا RESET در هرلحظه تحت سوئیچینگ معمولی فعال باشد و در نتیجه شرایط نامعتبری را که قبلاً در فلیپ فلاپ SR مشاهده شده بود حذف میکند. جریان. با این حال، اگر هر دو ورودی J و K در منطق “1” (J = K = 1) HIGH باشند، هنگامی که ورودی ساعت HIGH میشود، مدار با سوئیچ کردن خروجیها تغییر حالت میدهد و حالت مکمل یکدیگر را تغییر میدهد.

این باعث میشود که فلیپ فلاپ JK بیشتر شبیه فلیپ فلاپ ضامن نوع T عمل کند زمانی که هر دو ترمینال “HIGH” هستند. با این حال، همانطور که خروجی ها به ورودی ها باز می گردند، این میتواند باعث شود خروجی در Q پس از یک بار تکمیل شدن، به طور مداوم بین SET و RESET نوسان کند.

در حالی که این مدار فلیپ فلاپ JK یک بهبود در فلیپ فلاپ SR کلاک شده است، اما اگر خروجی Q قبل از اینکه پالس زمان ورودی ساعت “خاموش” شود، حالت را تغییر دهد، از مشکلات زمان بندی به نام “مسابقه” نیز رنج میبرد. برای جلوگیری از این امر، دوره پالس زمانبندی (T) باید تا حد امکان کوتاه باشد (فرکانس بالا).

از آنجایی که گاهی اوقات این کار با JK های اولیه ساختهشده با استفاده از گیت های NAND یا NOR امکان پذیر نیست، فلیپ فلاپ های master-slave بسیار پیشرفته تری ساخته شدهاند که پایدارتر هستند.

فلیپ فلاپ master-slave با استفاده از دو فلیپ فلاپ SR که در یک پیکربندی سری به هم متصل شدهاند، تمام مشکلات زمانبندی را از بین میبرد. یک فلیپ فلاپ به عنوان مدار “Master” عمل میکند که در لبه جلوی پالس ساعت فعال میشود در حالی که دیگری به عنوان مدار “Slave” عمل میکند که در لبه سقوط پالس ساعت فعال میشود. این باعث میشود که دو بخش، بخش اصلی و بخش slave در طول نیم چرخه های مخالف سیگنال ساعت فعال شوند.

TTL 74LS73 یک آی سی فلیپ فلاپ دوگانه JK است که شامل دو بیستابل از نوع JK جداگانه در یک تراشه است که امکان ساخت فلیپ فلاپ های ضامن تک یا اصلی را فراهم میکند. از دیگر این آی سی ها میتوان به فلیپ فلاپ 74LS107 Dual JK با شفاف، 74LS109 دو فلیپ فلاپ با لبه مثبت JK و فلیپ فلاپ با لبه منفی دوگانه 74LS112 با ورودیهای از پیش تعیین شده و روشن اشاره کرد.

فلیپ فلاپ Master-Slave اساساً دو فلیپ فلاپ SR دردار است که در یک پیکربندی سری به هم متصل شدهاند و slave دارای یک پالس ساعت معکوس است.خروجیهای Q و Q بار از فلیپ فلاپ “Slave” به ورودیهای “Master” با خروجی های “Master” فلیپ فلاپ به دو ورودی فلیپ فلاپ “Slave” متصل میشوند.این پیکربندی بازخورد از خروجی Slave به ورودی Master تغییر مشخصه را مطابق شکل زیر میدهد.

سیگنال های ورودی J و K به فلیپ فلاپ SR “master” متصل هستند که شرایط ورودی را “قفل میکند” در حالی که ورودی ساعت (Clk) “HIGH” در سطح منطقی “1” است. از آنجایی که ورودی ساعت فلیپ فلاپ “slave” معکوس (مکمل) ورودی ساعت “master” است، فلیپ فلاپ SR “slave” تغییر نمیکند. خروجی های فلیپ فلاپ “master” تنها زمانی که ورودی ساعت “LOW” به سطح منطقی “0” میرود توسط فلیپ فلاپ “slave” دردار “دیده میشود”.

هنگامی که ساعت “LOW” باشد، خروجی های فلیپ فلاپ “master” قفل میشوند و هرگونه تغییر اضافی در ورودیهای آن نادیده گرفته میشود. فلیپ فلاپ دردار “slave” اکنون به وضعیت ورودیهای خود توسط بخش “master” پاسخ میدهد. سپس در انتقال “کم به بالا” پالس ساعت، ورودیهای فلیپ فلاپ “master” به ورودی های گیت فلیپ فلاپ “slave” و در انتقال “بالا به پایین” تغذیه میشوند. همان ورودیها روی خروجی «slave» منعکس میشوند و این نوع لبه فلیپ فلاپ یا پالس راهاندازی میکنند.

سپس، مدار زمانی که سیگنال ساعت “HIGH” باشد، دادههای ورودی را میپذیرد و داده ها را به خروجی روی لبه سقوط سیگنال ساعت ارسال میکند؛ به عبارت دیگر، فلاپ فلاپ Master-Slave JK یک دستگاه “همگام” است زیرا فقط داده ها را با زمان بندی سیگنال ساعت ارسال میکند.